Financial applications run time can be expedited by factors of up to 20x. Data center footprint – TCO and energy consumption – would potentially be reduced by unprecedented 80% or more; depending on their DFP operations percent.

SilMinds core units can be combined in a reconfigurable way to optimize the arithmetic operations execution pipes with respect to the specific application’s native computing patterns.

Learn more about SilMinds IP core DFPA units…

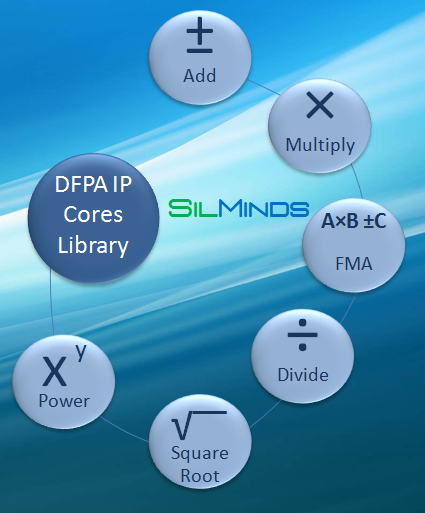

SilMinds Decimal IP family presents new designs for decimal floating point (DFP) addition, multiplication, fused multiply-add division, and square root. Our products emphasize the importance of energy savings achieved by hardware implementations of the IEEE 754-2008 standard for decimal floating point.

SilMinds is the first company worldwide to discuss energy savings in DFP and the first to present a hardware implementation of a fused multiply-add function. Our Newton-Raphson based divider is over three times faster than the similar design previously reported.

A presentation of decimal arithmetic technology can be downloaded here.

DFPA Family Cores

• DecAdd64/128 – Decimal Adder units supporting decimal64 and decimal128 formats

• DecMult64/128 – Decimal Multiplier units supporting decimal64 and decimal128 formats

• DecFMA64/128 – Decimal Fused Multiplier-Adder units supporting decimal64 and decimal128 formats

• NRDecDiv64/128 – Decimal Divider units supporting decimal64 and decimal128 formats

• NRDecSqrt64/128 – Decimal Square Root units supporting decimal64 and decimal128 formats

Key Features

• Full IEEE 754-2008 compliance, supporting Decimal64 (16 digits) and decimal128 (34 digits)

• Decimal Interchange format encoding with Densely Packed Decimal (DPD) coding support

• Combinational or pipelined versions are available

• Seven rounding modes support

• Tested with over 500,000 test cases compliant with IEEE 754-2008 format

• Full floating point precision support

• Fully synthesizable with no internal tri-states

IP Deliverable

The IP deliverable is highly dependent on the type of licensing agreement and the business model. Depending on the negotiated business model, the following deliverable might be included.

• Source code:

o VHDL Source Code

o VERILOG Source Code available upon special request

o Encrypted (or plain text) EDIF netlist

• VHDL/VERILOG test bench environment

• Full test suites compliant with IEEE 754-2008 standard

• Technical documentation

• HDL core specification

• Product data sheets

• Synthesis scripts

• Technical support

• IP Core deployment support