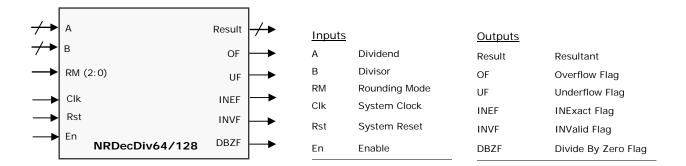

# IP Core Product Data Sheet DFP Newton-Raphson Divider Units NRDecDiv64/128

NRDecDiv64 and NRDecDiv128 IP core units are novel DFP Divider designs, offered in 64-bit and 128-bit versions. The unit computes the Quotient of two vector Operands. Inputs are encoded in Decimal Interchange Format.

The Divider is based on the Newton-Raphson iterative method. It computes the final quotient in 2 iterations for the 64-bit version and in 3 iterations for the 128-bit version. The product is fully compliant with the IEEE 754-2008 Standard.

# **Key Features**

- ⇒ Full IEEE 754-2008 compliance

- ⇒ Decimal128 (34 decimal digits) format support

- ⇒ Decimal Interchange format with Densely Packed Decimal (DPD) encoding support

- ⇒ Seven rounding modes support

- $\Rightarrow$  Result is available at every clock cycle

- ⇒ Overflow, Underflow, Invalid, and Inexact operation flags

- ⇒ Tested with over 500,000 test cases compliant with IEEE 754-2008 format

- $\Rightarrow$  Full DFP accuracy and precision support

- ⇒ Fully synthesizable with no internal tri-states

### **Applications**

- ⇒ DFPA units for next generation processors

- ⇒ DFPA on-chip co-processors

- ⇒ DFPA accelerator boards

### **IP** Deliverable

Deliverable depends on the type of licensing agreement and the negotiated business model. The following items could be included:

- ⇒ Source code:

- VHDL source code

- VERILOG source code

- Encrypted or plain text EDIF netlist

- ⇒ FPGA code versions, optimized for either speed or area

- ⇒ VHDL & VERILOG test bench environments

- ⇒ Full test suites compliant with IEEE 754-2008 standard.

- ⇒ Technical documentation

- ⇒ HDL core specification

- $\Rightarrow$  Synthesis scripts

- $\Rightarrow$  IP Core implementation support

### **Performance Data**

The table below summarizes gate-level synthesized performance data in TSMC 90 nm, for sample combinational designs. More detailed performance data can be found in the product technical documentation.

| Design           | Cycle Delay |       | Nr. of | <u>Area</u> |         |

|------------------|-------------|-------|--------|-------------|---------|

|                  | nS          | FO4   | Cycles | μm²         | NAND2   |

| NRDecDiv64-comb  | 2.62        | 58.22 | 11     | 425,198.1   | 150,652 |

| NRDecDiv128-comb | 3.20        | 71.11 | 13     | 880,243.1   | 311,878 |

# Configurations

NRDecDiv64/128 can be combined with other SilMinds IP core units to comprise arbitrary decimal coprocessor architectures. Deployment is made easy and reliable through a compact core size, parameterized RTL, and flexible test benches.

# **Product Verification**

This product has been verified using an innovative and efficient constraint driven test vector generation tool. The test vectors cover all valid cases in conformance with the IEEE 754-2008 standard.

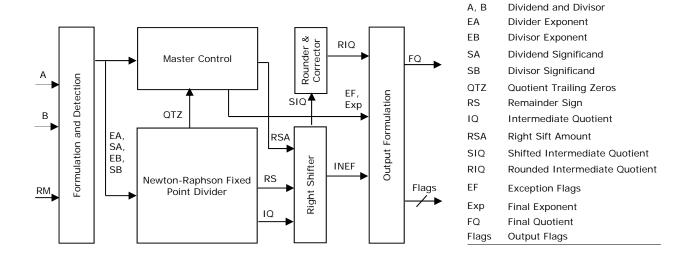

### Symbol & Block Diagram

# **Divider Unit Functions**

## Formulation & Detection

- Decodes input operands (Dividend and Divisor) using IEEE 754-2008 format to produce the sign bit, significand, and exponent

- Performs special input detection (infinity or NaN)

- Performs significand normalization

### **Master Control**

Generates the result exponent (computed to be the preferred exponent as defined by the IEEE 754-2008), the output flags, and a number of control signals

# Right Shifter

Removes excess trailing zeroes

## **Fixed Point Divider**

Performs decimal fixed point division, based on the Newton-Raphson iterative method, employing a novel parallel decimal fixed multiplier to reduce

### **Rounder & Corrector**

Performs quotient rounding to fit in the required precision

# **Output Formulation**

- Encodes the resultant significand in DPD format

- Formulates the special values (infinity or NaN) to comply with the IEEE 754-2008 standard

- Sets the appropriate flags